先决条件 – 计数器

问题 –为序列设计同步计数器:0 → 1 → 3 → 4 → 5 → 7 → 0,使用 T 触发器。

说明——对于给定的序列,状态转换图如下:

状态转移表逻辑:

| Present State | Next State |

|---|---|

| 0 | 1 |

| 1 | 3 |

| 3 | 4 |

| 4 | 5 |

| 5 | 7 |

| 7 | 0 |

给定序列的状态转换表:

| Present State | Next State | ||||

|---|---|---|---|---|---|

| Q3 | Q2 | Q1 | Q3(t+1) | Q2(t+1) | Q1(t+1) |

| 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 |

T 触发器 –如果 Q 的值从 0 变为 1 或从 1 变为 0,则 T 触发器的输入为 1,否则输入值为 0。

| Qt | Qt+1 | T |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

用T触发器的激励表画出所有T触发器的输入表。由于 T 触发器的性质本质上是切换。这里,Q3 作为最高有效位,Q1 作为最低有效位。

| Input table of Flip-Flops | |||

|---|---|---|---|

| T3 | T2 | T1 | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 1 | 1 | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 1 | 1 | |

使用 K-Map(卡诺图)根据 Q 3 、Q 2 、Q 1求出 T 3 、T 2 、T 1 的值:

所以,

T3 = Q2

所以,

T2 = Q1

所以,

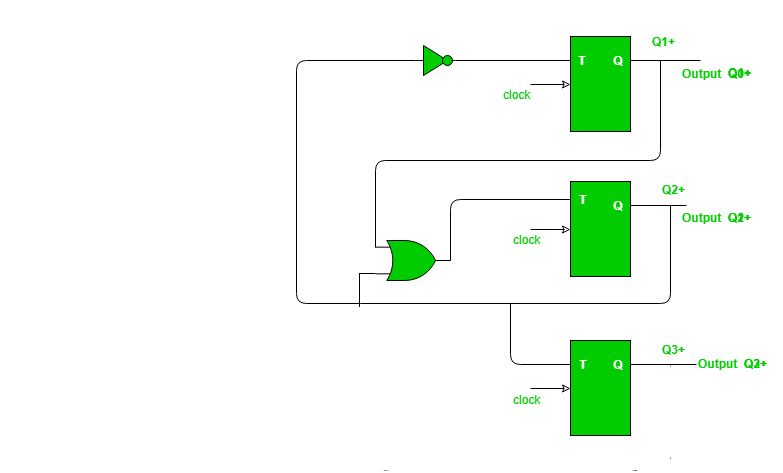

T1 = Q2’ 现在,您可以使用 K-map 的表达式设计所需的电路: