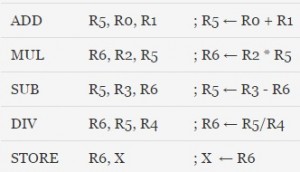

流水线处理器使用具有以下阶段的4级指令流水线:指令提取(IF),指令解码(ID),执行(EX)和写回(WB)。算术运算以及装入和存储运算在EX阶段中执行。下面给出与语句X =(SR – R *(P + Q))/ T对应的指令序列。在执行指令序列之前,变量P,Q,R,S和T的值分别在寄存器R 0 ,R 1 ,R 2 ,R 3和R 4中可用。

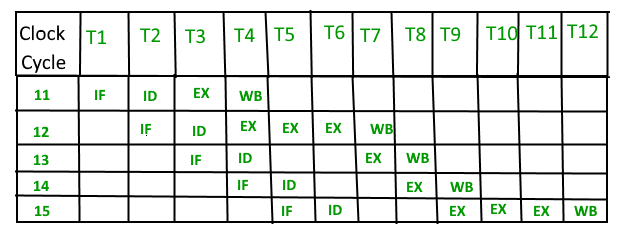

IF,ID和WB级分别占用1个时钟周期。 EX级分别对ADD,SUB和STORE操作花费1个时钟周期,对MUL和DIV操作分别花费3个时钟周期。使用从EX阶段到ID阶段的操作数转发。完成指令序列所需的时钟周期数为

(A) 10

(B) 12

(C) 14

(D) 16答案: (B)

解释:

流水线化是一种通过执行指令的不同阶段来并行执行指令的技术。

通常,如果执行了两个操作,其中第二个操作首先具有从属操作数,则第二个操作应在第一个操作执行之前不获取操作数,否则它将获取不正确的操作数。因此,创建了档位。

现在,为了克服这个问题,引入了操作数转发技术,该技术中存在一个接口,通过该接口可以传输操作数结果。因此,即使在执行阶段的提取操作期间提取了错误的操作数,错误的操作数也会被替换为

正确的操作数。

因此,在给定的问题中,尽管由于R5导致MUL依赖于ADD,由于R6导致SUB依赖于MUL,而DIV取决于SUB和STORE取决于DIV,我们仍然可以在流水线处理器中执行指令获取和解码操作。

在哪里,

IF指令提取

ID指令解码

EX执行

WB写回

如表中所示,将采用12个时钟周期来执行给定的指令。

此解决方案由Shashank Shanker khare提供

这个问题的测验