先决条件–并行计算简介

指令级并行(ILP)用于指这样的体系结构,在该体系结构中,可以在特定进程中使用其自己的资源(地址空间,寄存器,标识符,状态,程序计数器)并行执行多个操作。它指的是编译器设计技术和处理器,旨在并行执行操作(例如内存加载和存储,整数加法,浮点乘法)以提高处理器性能。利用ILP的体系结构示例包括VLIW(超标量体系结构)。

ILP处理器与RISC处理器具有相同的执行硬件。没有ILP的机器具有复杂的硬件,难以实施。典型的ILP允许流水线化多周期操作。

例子 :

假设可以在一个时钟周期内执行4次操作。因此,将有4个功能单元,每个功能单元都附加到ILP执行硬件中的操作,分支单元和公用寄存器文件之一。功能单元可以执行的子操作是整数ALU,整数乘法,浮点运算,加载,存储。令各自的等待时间为1、2、3、2、1。

让指令的顺序为–

- y1 = x1 * 1010

- y2 = x2 * 1100

- z1 = y1 + 0010

- z2 = y2 + 0101

- t1 = t1 + 1

- p = q * 1000

- clr = clr + 0010

- r = r + 0001

顺序执行记录与指令级并行执行记录–

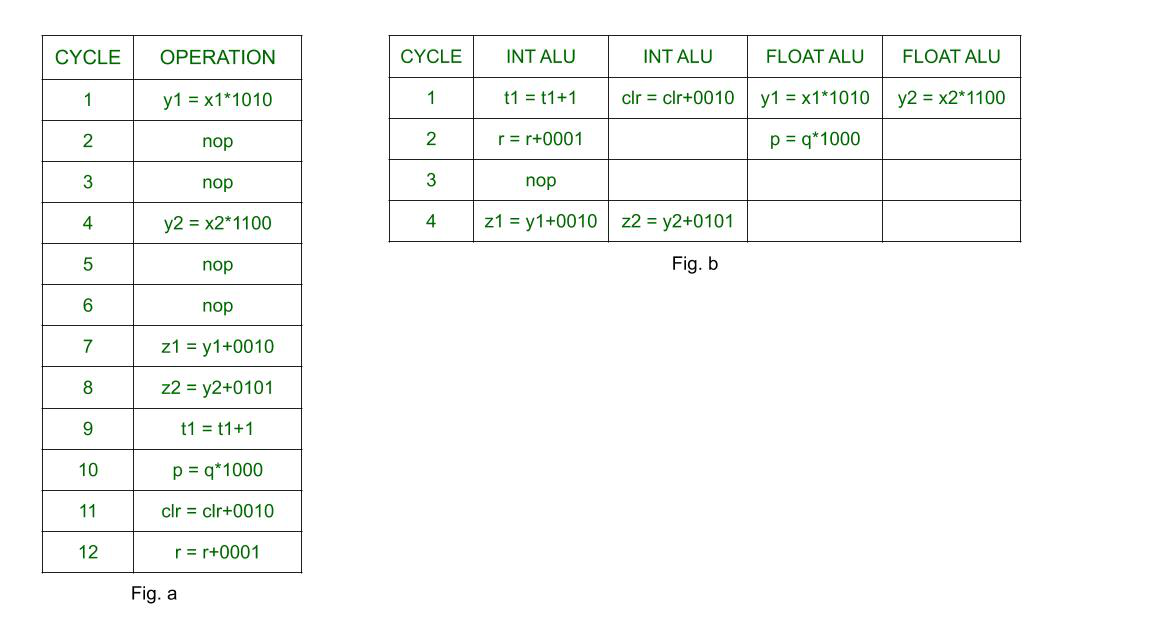

图a示出了操作的顺序执行。

图b显示了ILP在改善处理器性能方面的使用。

上图中的“ nop”或“ no operation”用于显示处理器的空闲时间。由于浮点运算的等待时间为3,因此乘法需要3个周期,并且处理器必须在该时间段内保持空闲状态。然而,在图b中,处理器可以利用那些nop来执行其他操作,同时仍在执行先前的操作。

在顺序执行中,每个周期仅执行一个操作,在具有ILP的处理器中,周期1具有4个操作,周期2具有2个操作。在循环3中,出现“ nop”,因为接下来的两个运算取决于前两个乘法运算。顺序处理器需要12个周期来执行8个操作,而具有ILP的处理器仅需要4个周期。建筑学 :

当在单个周期中执行多个操作时,即可以同时执行多个操作,也可以利用由于延迟而产生的两个连续操作之间的间隙来实现指令级并行性。

现在,何时执行操作的决定很大程度上取决于编译器,而不是硬件。但是,编译器的控制范围取决于ILP体系结构的类型,在ILP体系结构中,有关编译器通过程序提供给硬件的并行性的信息会有所不同。 ILP体系结构的分类可以通过以下方式进行:

- 顺序架构:

在这里,不希望程序明确地将任何有关并行性的信息传达给硬件,例如超标量体系结构。 - 依赖架构:

在这里,程序明确提到有关数据流体系结构之类的操作之间的依赖关系的信息。 - 独立架构:

在此,程序给出有关哪些操作彼此独立的信息,以便可以代替“ nop”执行这些操作。

为了应用ILP,编译器和硬件必须确定数据依赖关系,独立操作以及这些独立操作的调度,功能单元的分配以及用于存储数据的寄存器。