📌 相关文章

- 嵌入式系统的体系结构|套装3

- 嵌入式系统的体系结构|套装3

- 嵌入式系统项目

- 嵌入式系统项目(1)

- 嵌入式系统-I / O编程

- 嵌入式系统C编程

- 嵌入式系统C编程(1)

- 嵌入式系统I/O编程

- 嵌入式系统教程

- 嵌入式系统教程(1)

- 嵌入式系统的设计(1)

- 嵌入式系统的设计

- 讨论嵌入式系统

- 讨论嵌入式系统(1)

- 嵌入式系统-概述

- 嵌入式系统的分类(1)

- 嵌入式系统的分类

- 嵌入式系统的分类

- 嵌入式实时系统(1)

- 嵌入式实时系统

- 嵌入式系统的优缺点

- 嵌入式系统的优缺点(1)

- 嵌入式系统-术语(1)

- 嵌入式系统-术语

- 嵌入式系统-处理器

- 嵌入式系统处理器

- 嵌入式系统处理器(1)

- 嵌入式系统-处理器(1)

- 计算机与嵌入式系统的区别

📜 嵌入式系统-体系结构类型

📅 最后修改于: 2021-01-07 05:43:22 🧑 作者: Mango

8051微控制器使用8位数据总线。因此,它们最多可以支持高达64K的外部数据存储器和64k的外部程序存储器。总的来说,8051微控制器可以寻址128k的外部存储器。

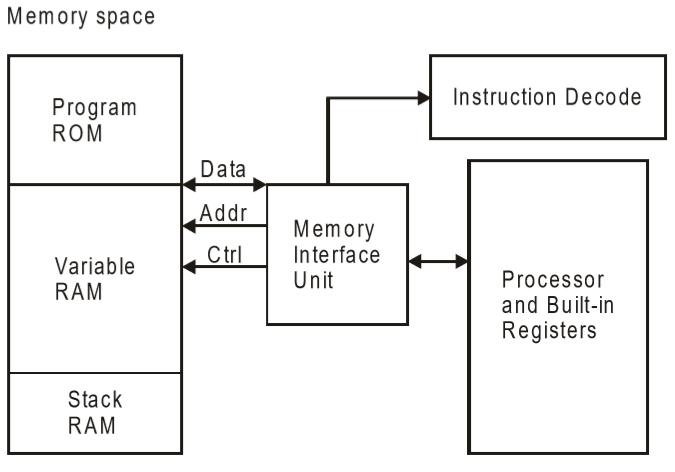

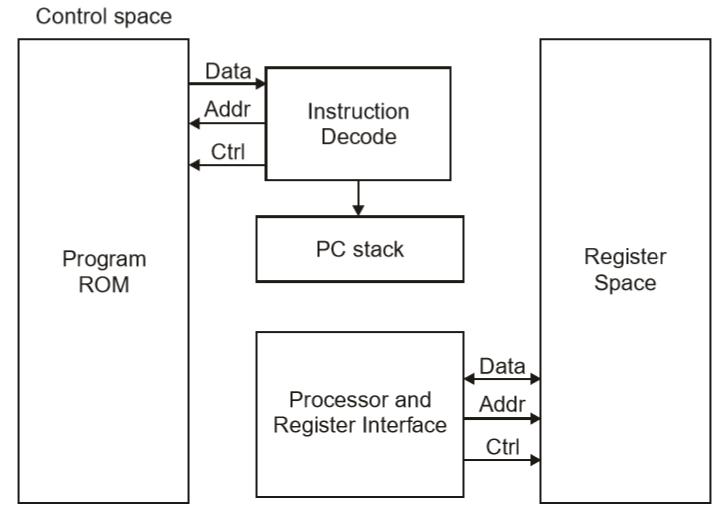

当数据和代码位于不同的存储块中时,该架构称为哈佛架构。如果数据和代码位于同一存储块中,则该架构称为Von Neumann架构。

冯·诺依曼建筑

冯·诺依曼架构最早是由计算机科学家约翰·冯·诺依曼提出的。在这种体系结构中,一条数据路径或总线用于指令和数据。结果,CPU一次执行一项操作。它要么从内存中获取一条指令,要么对数据执行读/写操作。因此,共享公共总线不能同时进行指令获取和数据操作。

冯·诺依曼架构支持简单的硬件。它允许使用单个顺序存储器。当今的处理速度大大超过了内存访问时间,并且我们在处理器本地采用了非常快速但数量很少的内存(高速缓存)。

哈佛建筑

哈佛架构为指令和数据提供了单独的存储和信号总线。这种体系结构的数据存储完全包含在CPU中,并且不能以数据形式访问指令存储。计算机具有使用内部数据总线的程序指令和数据的独立存储区,从而可以同时访问指令和数据。

程序需要由运算符加载;处理器无法自行启动。在哈佛架构中,无需使两个内存共享属性。

冯·诺依曼架构与哈佛架构

以下几点将冯·诺依曼架构与哈佛架构区分开。

| Von-Neumann Architecture | Harvard Architecture |

|---|---|

| Single memory to be shared by both code and data. | Separate memories for code and data. |

| Processor needs to fetch code in a separate clock cycle and data in another clock cycle. So it requires two clock cycles. | Single clock cycle is sufficient, as separate buses are used to access code and data. |

| Higher speed, thus less time consuming. | Slower in speed, thus more time-consuming. |

| Simple in design. | Complex in design. |

CISC和RISC

CISC是复杂指令集计算机。这是一台可以处理大量指令的计算机。

在1980年代初期,计算机设计人员建议计算机应使用较少的具有简单结构的指令,以便可以在CPU内更快地执行它们而不必使用内存。这样的计算机被归类为精简指令集计算机或RISC。

CISC与RISC

以下几点将CISC与RISC区别开来-

| CISC | RISC |

|---|---|

| Larger set of instructions. Easy to program | Smaller set of Instructions. Difficult to program. |

| Simpler design of compiler, considering larger set of instructions. | Complex design of compiler. |

| Many addressing modes causing complex instruction formats. | Few addressing modes, fix instruction format. |

| Instruction length is variable. | Instruction length varies. |

| Higher clock cycles per second. | Low clock cycle per second. |

| Emphasis is on hardware. | Emphasis is on software. |

| Control unit implements large instruction set using micro-program unit. | Each instruction is to be executed by hardware. |

| Slower execution, as instructions are to be read from memory and decoded by the decoder unit. | Faster execution, as each instruction is to be executed by hardware. |

| Pipelining is not possible. | Pipelining of instructions is possible, considering single clock cycle. |