同步计数器:它是一种数字电路,借助触发器和同时触发的所有触发器以二进制数进行计数。

给定计数序列的同步计数器设计程序:

- 确定计数序列所需的触发器 (FF)、输入和输出的数量。

- 选择要使用的 FF 类型。

- 构造包含计数器当前状态和下一状态的状态表以及所用FF的激励表。

- 找出 FF 的每个输入的方程或表达式。这里我们可以使用提供最小化表达的 K-map 方法。

- 现在根据在步骤 4 中获得的表达式在使用的 FF 和门之间建立连接。

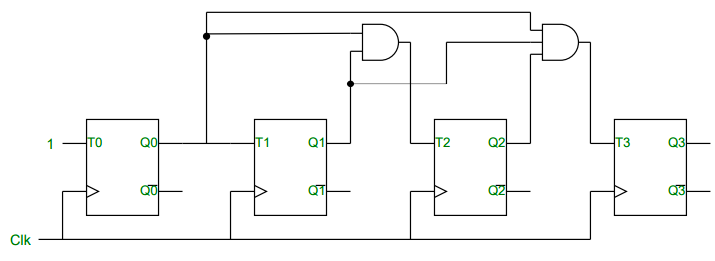

示例– 首先,我们将使用 T-FF 实现一个 4 位同步递增计数器。所以,我们需要 4 个 FF,分别是 FF0、FF1、FF2 和 FF3。它可以从 0 到 15(16 个数字)计数。以下是该计数器使用 T-FF 的激励表的表格,

|

Current state |

Next state |

Input to FFs |

|||||||||

| Q3 | Q2 | Q1 | Q0 | Q3 | Q2 | Q1 | Q0 | T3 | T2 | T1 | T0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

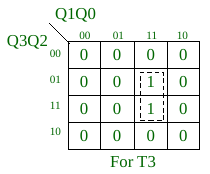

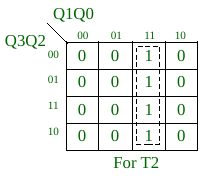

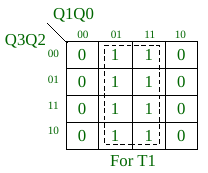

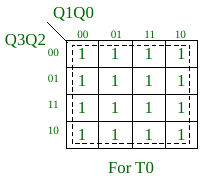

使用 K-map,我们可以找到 T0、T1、T2 和 T3 的布尔表达式。

所以, T0 = 1,

T1 = Q0,

T2 = Q0.Q1,

T3 = Q0.Q1.Q2,

4-bit Synchronous Series-Carry Up Counter : 对于上面的例子,我们可以使用这个link(article)来实现series-carry counter。而在这个串联进位计数器中,所有使用的与门的扇入值(输入数)都是2,并且是固定的。

为什么我们需要同步并行进位计数器而不是同步串联进位计数器? 如果我们在上面的例子中看到串行进位计数器的实现,它的与门使用其他一些与门的输出。如上述获得的表达,其产生Q0.Q1.Q2与门可以使用的AND门的输出产生Q0.Q1,或我们可以写出T3 = T2.Q2。这同样可以应用于更高计数的序列。这种安排会导致计数器电路电平的增加。高电平意味着电路稳定状态需要更多时间。同样的事情我们可以在上面的链接中看到,计数增加一个的延迟取决于 FF 的数量。因此,我们使用同步并行进位计数器,降低了电路的电平。

4 位同步并行进位计数器:

对于上面给出的例子

逻辑图-

时序图-

这里,

T clk >= t ff + t g , n>=3 ………………. (一种)

在哪里

- T clk — 使用的时钟周期。

- t ff — FF 完成其操作所需的时间。

- t g — 任何门完成其操作所需的最长时间。

- n — 使用的 FF 数量。

并行进位计数器背后的想法——在这个设计中,我们尝试实现一个只有 2 电平的电路。第一级为 FF 保留,第二级用于执行电路中使用的门。无论计数顺序如何,并行进位计数器始终保持在 2 电平电路中,但串联进位计数器随着计数数量的增加而增加电平。我们可以说同步并行进位计数器比同步串行进位计数器快得多。

优点:在等式(a)中,时间段与FF数或计数数(如果n>=3)无关。因此,无论计数序列的大小如何,时钟的时间周期都将保持不变。但是,这在串联进位计数器的情况下是不可能的。这是同步并行进位计数器相对于同步串联进位计数器的主要优点。

缺点:计数器中使用的与门的扇入值(输入数量)随着 FF 的数量线性增加。对于计数器中的 n 个 FF,我们需要扇入值从 2 到 n-1 的与门。并且实际上不存在具有更高扇入值的门。因此,对于较少计数序列大小,并行进位计数器比串联进位计数器好得多,但对于高计数序列大小则不然。

关于上述示例的同步并行进位和串行进位计数器的一些事实

- 我们可以看到,对于相同的计数数字,两个计数器所需的门数是相同的。

- 以上两个计数器都使用了与门,但门的类型可以根据计数顺序改变。这完全取决于我们在程序的步骤 4 中为 FF 的所有输入获得的最小化表达式。例如,环形计数器是一个同步计数器,但没有使用任何与门或其他门。

尽量减少并行进位和串联进位计数器的缺点的策略

我们可以通过结合上述两个计数器的特点来制作一个计数器。例如,我们可以使用新的门,它使用其他门的一些值作为串联进位计数器,但它的扇入值比并行进位计数器中与此相对应的门少。例如,一个有 n 个 FF 且 n 更高的计数器,串联进位计数器将有 n-1 级(FF 为 1,门为 n-2),并行进位计数器将有一个 2 级电路,现在我们可以实现用于电平接近 n/2 的计数器的电路。该策略适用于给定示例中类型的计数序列。