表示和存储数字是早期计算机的基本操作。当计算、加法、乘法等操作数字出现时,真正的开始出现了。这些操作由计算机的算术逻辑单元 (ALU) 处理。 ALU 是计算机的数学大脑。第一个 ALU 是 INTEL 74181,作为 7400 系列实现,是 1970 年发布的 TTL 集成电路。

ALU是提供算术和逻辑运算的数字电路。它是计算机中央处理单元的基本构建块。现代 CPU 具有非常强大的 ALU,并且设计复杂。除了 ALU 现代 CPU 还包含一个控制单元和一组寄存器。大多数操作由一个或多个 ALU 执行,它们从输入寄存器加载数据。寄存器是 CPU 可用的少量存储空间。这些寄存器的访问速度非常快。控制单元告诉 ALU 对可用数据执行什么操作。在计算/操作之后,ALU 将输出存储在输出寄存器中。

CPU可以分为两部分:数据部分和控制部分。 DATA 部分也称为数据路径。 BUS:在早期的计算机中,“BUS”是具有多个硬件连接的并行电线。因此,总线是一种在计算机内部组件之间或计算机之间传输数据的通信系统。它包括硬件组件(如电线、光纤等)和软件(包括通信协议)。寄存器、ALU 和互连总线统称为数据路径。

巴士的种类有:

- 地址总线:用于承载地址的总线。

- 数据总线:用于承载数据的总线。

- 控制总线:如果总线承载控制信号。

- 电源总线:如果它承载时钟脉冲、电源信号,则称为电源总线,依此类推。

总线可以是专用的,即它可以用于单一目的,也可以是多路复用的,即它可以用于多种目的。当我们拥有不同种类的巴士时,就会出现不同类型的巴士组织。

- 程序计数器 –

程序计数器 (PC) 是计算机处理器中的 CPU 寄存器,它具有要从内存中执行的下一条指令的地址。当获取每条指令时,程序计数器将其存储值增加 1。它是一个数字计数器,用于更快地执行任务以及跟踪当前执行点。 - 指令寄存器 –

在计算中,指令寄存器 (IR) 是 CPU 控制单元的一部分,用于保存当前正在执行或解码的指令。指令寄存器是 CPU 控制单元的一部分,用于保存当前正在执行或解码的指令。指令寄存器专门保存指令并将其提供给指令解码器电路。 - 内存地址寄存器 –

内存地址寄存器 (MAR) 是 CPU 寄存器,用于存储将从 CPU 获取数据的内存地址,或将发送和存储数据的地址。它是CPU(中央处理单元)中的一个临时存储组件,用于临时存储内存单元发送的数据的地址(位置),直到执行特定数据的指令。 - 内存数据寄存器 –

内存数据寄存器 (MDR) 是计算机处理器或中央处理单元 CPU 中的寄存器,用于存储传入和传出即时存取存储器的数据。内存数据寄存器 (MDR) 也称为内存缓冲寄存器 (MBR)。 - 通用寄存器 –

通用寄存器用于在微处理器内存储临时数据。它是一个多用途寄存器。它们可以由程序员或用户使用。

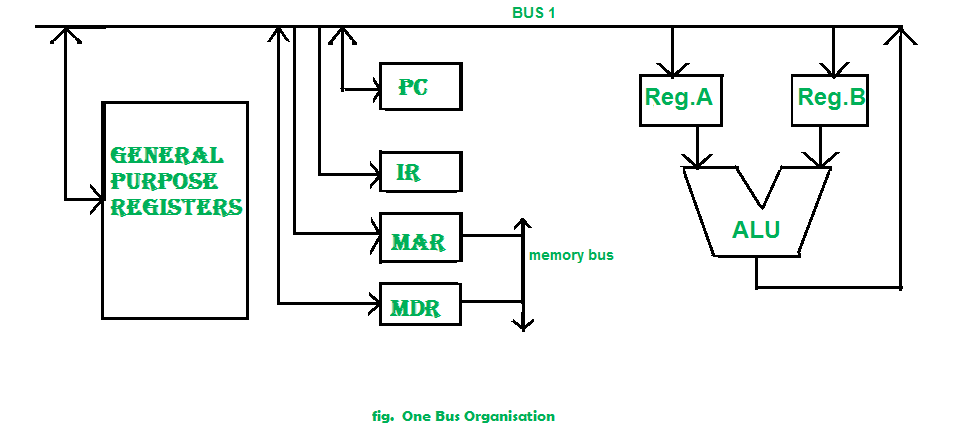

一个巴士组织 –

在一个总线组织中,一条总线用于多种用途。一组通用寄存器、程序计数器、指令寄存器、内存地址寄存器(MAR)、内存数据寄存器(MDR)与单总线相连。内存读/写可以通过 MAR 和 MDR 来完成。程序指向要从中获取下一条指令的内存位置。指令寄存器是那个寄存器将保存当前指令的副本。在一个总线组织的情况下,一次只能从总线读取一个操作数。

因此,如果操作要求读取两个操作数,则读取操作需要进行两次。所以这就是为什么它使过程更长一些。一种总线组织的优点之一是它是最简单的组织之一,而且实施起来非常便宜。同时一个缺点是它只有一条总线,这个“一条总线”被所有的通用寄存器、程序计数器、指令寄存器、MAR、MDR访问,使得每一个操作都是顺序的。现在没有人推荐这种架构。两个巴士组织 –

两个克服了一个总线组织的缺点,另一种架构被开发出来,称为两个总线组织。在两个总线组织中,有两条总线。通用寄存器可以从两条总线读/写。在这种情况下,因为有两条总线,所以可以同时取两个操作数。一个总线获取操作数用于 ALU,另一个总线获取操作数用于寄存器。当两条总线都忙于获取操作数时,就会出现这种情况,输出可以存储在临时寄存器中,而当总线空闲时,特定的输出可以转储到总线上。

两种总线组织有两种版本,即in-bus 和out-bus。从in-bus,通用寄存器可以读数据,到out总线,通用寄存器可以写数据。这里的巴士是专用的。

三总线组织——

在三个总线组织中,我们有三个总线,OUT bus1、OUT bus2 和 IN bus。从输出总线,我们可以得到可以来自通用寄存器并在 ALU 中计算的操作数,输出被丢弃在输入总线上,因此它可以发送到相应的寄存器。这种实现有点复杂,但本质上更快,因为两个操作数可以并行流入 ALU 和流出 ALU。它的开发是为了克服两个总线组织的“忙等待”问题。在这个结构中执行后,由于存在额外的总线,输出可以被丢弃在总线上而无需等待。结构如下图所示。

多总线组织相对于单总线的主要优点如下。

- 增加寄存器的大小。

- 减少执行周期数。

- 提高执行速度,或者我们可以说执行速度更快。