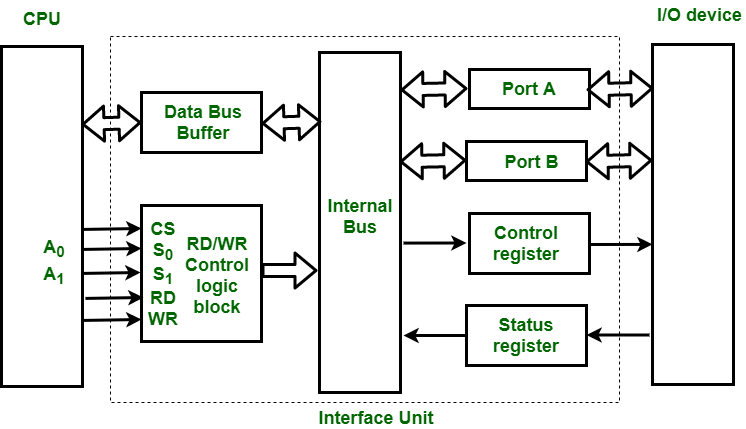

输入输出接口单元的框图包含以下块:

1. Data Bus Buffer

2. Read/Write Control Logic

3. Port A, Port B register

4. Control and Status register

这些解释如下。

数据总线缓冲区:

总线缓冲区使用双向数据总线与CPU进行通信。接口单元和CPU之间的所有控制字数据和状态信息都通过数据总线传输。

港口A和港口B:

端口A和端口B用于在输入输出设备和接口单元之间传输数据。每个端口包括双向数据输入缓冲区和双向数据输出缓冲区。接口单元直接与输入设备和输出磁盘连接,或者与需要通过端口A和端口B进行输入和输出的设备直接连接,即调制解调器,外部硬盘驱动器,磁盘。

控制和状态寄存器:

CPU基于控制信息将控制信息提供给控制寄存器。接口单元控制CPU和输入输出设备之间的输入和输出操作。状态寄存器中存在的位用于检查状态条件。状态寄存器指示数据寄存器,端口A,端口B的状态,并记录数据传输期间可能发生的错误。

读/写控制逻辑:

该模块生成整个设备操作所需的控制信号。通过此块可以接受来自CPU的所有命令。它还允许接口单元的状态通过该模块接收CS,来自系统总线的读写控制信号以及来自系统地址总线的S 0 ,S 1传输到数据总线上。读和写信号用于定义通过数据总线的数据传输方向。

Read Operation: CPU <---- I/O device

Write Operation: CPU ----> I/O device

读信号直接将数据从接口单元传输到CPU,写信号直接将数据从CPU传输到接口单元,通过数据总线。

地址总线用于选择接口单元。地址总线的两个最低有效线(A 0 ,A 1 )连接到选择线S 0 ,S 1 。这两条选择输入线用于选择接口单元中四个寄存器中的任何一个。根据以下标准选择接口单元:

读取状态:

| Chip Select | Operation | Select lines |

Selection of Interface unit |

||

|---|---|---|---|---|---|

| CS | Read | Write | S 0 |

S 1 |

|

| 0 | 0 | 1 | 0 | 0 | Port A |

| 0 | 0 | 1 | 0 | 1 | Port B |

| 0 | 0 | 1 | 1 | 0 | Control Register |

| 0 | 0 | 1 | 1 | 1 | Status Register |

写入状态:

| Chip Select | Operation | Select lines | Selection of Interface unit |

||

|---|---|---|---|---|---|

| CS | Read | Write | S 0 |

S 1 |

|

| 0 | 1 | 0 | 0 | 0 | Port A |

| 0 | 1 | 0 | 0 | 1 | Port B |

| 0 | 1 | 0 | 1 | 0 | Control Register |

| 0 | 1 | 0 | 1 | 1 | Status Register |

例子 :

- 如果S 0 ,S 1 = 0 1,则选择端口B数据寄存器在CPU和I / O设备之间进行数据传输。

- 如果S 0 ,S 1 = 1 0,则选择控制寄存器并存储CPU发送的控制信息。